19-3454; Rev 3; 4/06

EVALUATION KIT AVAILABLE

## Stereo Audio DAC with DirectDrive Headphone Amplifier

#### **General Description**

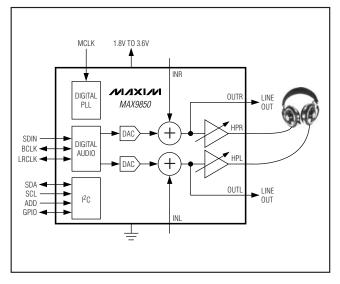

The MAX9850 is a low-power, high-performance stereo audio DAC with an integrated DirectDrive<sup>™</sup> headphone amplifier. The MAX9850 is designed to meet the board space and performance requirements of portable devices such as cell phones and MP3 and portable DVD players.

The MAX9850 uses Maxim's patented<sup>†</sup> DirectDrive headphone technology that produces a ground-biased analog audio output from a single supply, which allows for driving the headphones directly from the amplifier outputs without large DC-blocking capacitors. This feature saves board space, provides higher click/pop suppression, and improves low-frequency (bass) response. The architecture does not require the headphone jack to be biased to a DC voltage and thus allows for a conventional, grounded chassis design.

The MAX9850's flexible clocking circuitry utilizes any available system clock up to 40MHz, eliminating the need for an external PLL and multiple crystal oscillators. The DAC supports a wide range of sample rates from 8kHz to 48kHz in both master and slave modes, making the MAX9850 the easiest to use and most versatile audio DAC available. It can also be operated like traditional synchronous DACs, at any integer-oversampling ratio.

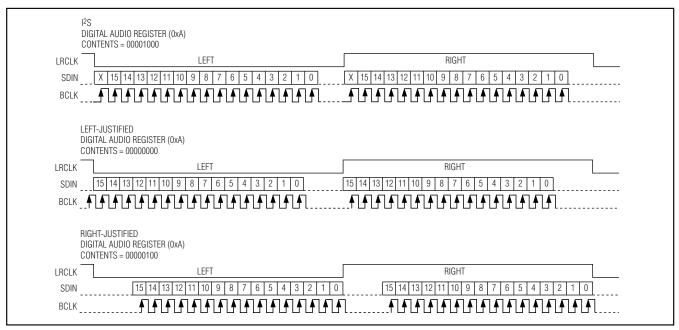

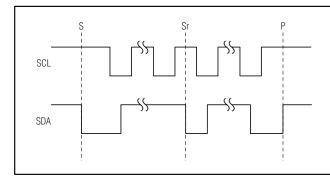

The audio DAC receives input data over a flexible 3-wire interface that supports left-justified, right-justified audio data, or  $l^2S$ -compatible audio data. Stereo audio line inputs are provided to either mix analog audio with the digital input stream, or to drive the headphone outputs directly. Mode settings, headphone amplifier volume controls, and shutdown for both the headphone and line outputs are programmed through a 2-wire,  $l^2C$ -compatible interface.

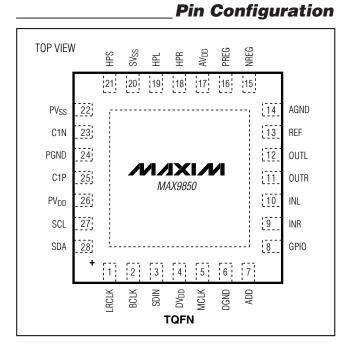

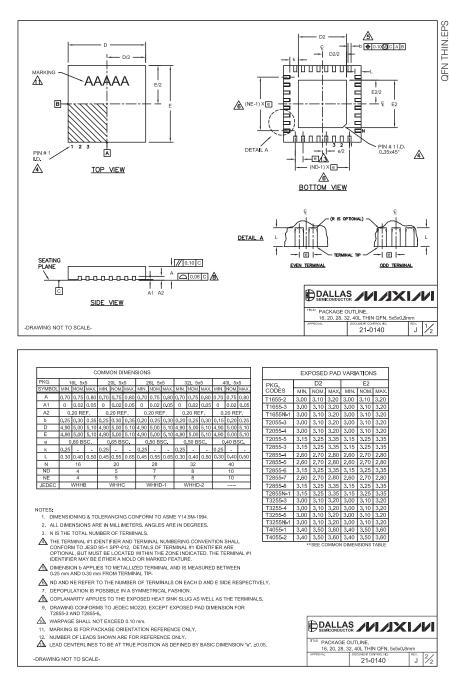

The MAX9850 is fully specified over the -40°C to +85°C extended temperature range and is available in a low-profile, 28-pin thin QFN package (5mm x 5mm x 0.8mm).

#### **Applications**

MP3/Portable Multimedia Players Cell Phones/Smart Phones Portable DVD Players

#### \_Features

- 1.8V to 3.6V Single-Supply Operation

- 30mW Stereo Headphone Output Power with 1.8V Supply

- DirectDrive Outputs Eliminate DC-Blocking Capacitors

- 91dB PSRR at 1kHz

- Any Master Clock Up to 40MHz

- ♦ Flexible I<sup>2</sup>S-Compatible Digital Audio Interface

- ♦ I<sup>2</sup>C Headphone Volume and Mute Control

- Stereo Line Inputs and Outputs

- Clickless/Popless Operation

- ♦ 2-Wire (I<sup>2</sup>C)-Compatible Control Interface

- Available in 28-Pin Thin QFN Package

#### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE  | PKG<br>CODE |

|-------------|----------------|--------------|-------------|

| MAX9850ETI+ | -40°C to +85°C | 28 TQFN-EP** | T2855-6     |

\*\*EP = Exposed pad.

+Denotes lead-free package.

Pin Configuration appears at end of data sheet.

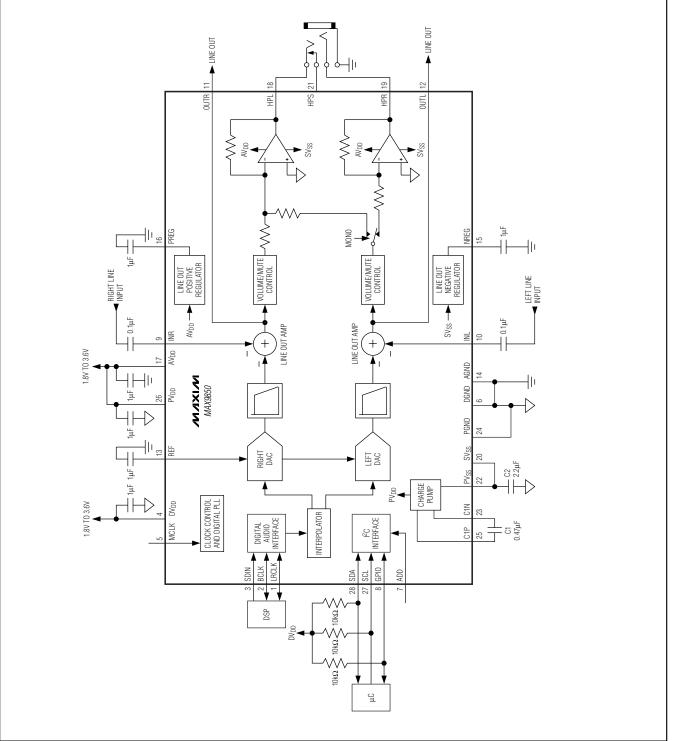

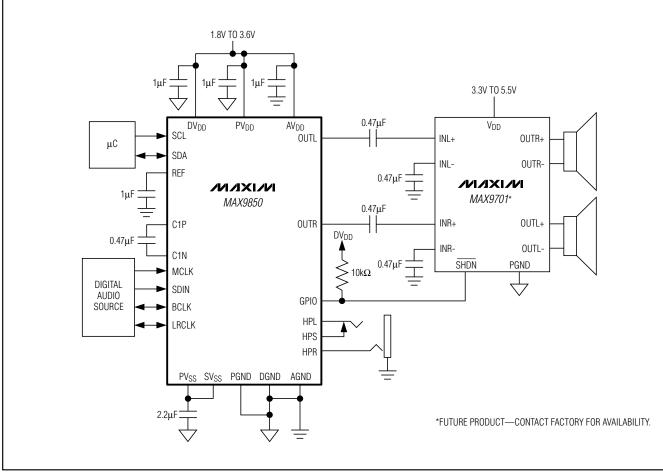

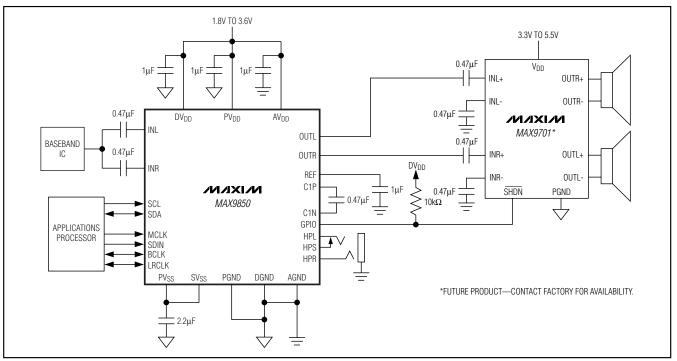

#### Block Diagram

†U.S. Patent #7,061,327

####

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

(Voltages with respect to AGND.)

| (                                                      |                                                        |

|--------------------------------------------------------|--------------------------------------------------------|

| DV <sub>DD</sub> , AV <sub>DD</sub> , PV <sub>DD</sub> | 0.3V to +4V                                            |

| AV <sub>DD</sub> Referenced to PV <sub>DD</sub>        | 0.3V to +0.3V                                          |

| SV <sub>SS</sub> , PV <sub>SS</sub>                    | 4V to +0.3V                                            |

| SV <sub>SS</sub> Referenced to PV <sub>SS</sub>        | 0.3V to +0.3V                                          |

| DGND, PGND                                             | 0.3V to +0.3V                                          |

| BCLK, LRCLK, HPS, SDIN                                 | 0.3V to (DV <sub>DD</sub> + 0.3V)                      |

|                                                        | 0.3V to +4V                                            |

| REF, PREG                                              | 0.3V to (AV <sub>DD</sub> + 0.3V)                      |

| NREG                                                   | +0.3V to (SV <sub>SS</sub> - 0.3V)                     |

| SDA, SCL, ADD                                          | -0.3V to +4V                                           |

| INL, INR                                               | 2V to +2V                                              |

| HPR, HPL                                               | (SV <sub>SS</sub> - 0.3V) to (AV <sub>DD</sub> + 0.3V) |

|                                                        |                                                        |

| OUTL, OUTR(NREG - 0.3V) to (PREG + 0.3V)<br>C1N(PV <sub>SS</sub> - 0.3V) to (PGND + 0.3V) |

|-------------------------------------------------------------------------------------------|

| C1P(PGND - 0.3V) to (PV <sub>DD</sub> + 0.3V)                                             |

| Current Into/Out of Any Pin100mA                                                          |

| Duration of HPL, HPR, OUTL,                                                               |

| OUTR Short Circuit to AGNDContinuous                                                      |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                     |

| 28-Pin Thin QFN (derate 35.7mW/°C above +70°C)2857mW                                      |

| Junction Temperature+150°C                                                                |

| Operating Temperature Range40°C to +85°C                                                  |

| Storage Temperature Range65°C to +150°C                                                   |

| Lead Temperature (soldering, 10s)+300°C                                                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(DV_{DD} = AV_{DD} = PV_{DD} = 3.0V, \ AGND = DGND = PGND = 0V, \ C1 = 0.47\mu\text{F}, \ C2 = 2.2\mu\text{F}, \ C_{NREG} = C_{PREG} = C_{REF} = 1\mu\text{F} \ to \ AGND, \ R_{LOAD\_HP} = 32\Omega \ to \ AGND, \ R_{LOAD\_OUT} = 10k\Omega \ to \ AGND, \ f_{LRCLK} = 48k\text{Hz}, \ f_{MCLK} = 12.288\text{MHz}, \ volume \ set \ to \ -9.5dB, \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. \ Typical \ specifications \ at \ T_A = +25^{\circ}\text{C}, \ unless \ otherwise \ noted.) \ (Note \ 1)$

| PARAMETER                           | SYMBOL                                 | CONDITIONS                                    |                  | MIN  | ТҮР  | MAX  | UNITS |

|-------------------------------------|----------------------------------------|-----------------------------------------------|------------------|------|------|------|-------|

| Analog Supply Voltage               | AV <sub>DD</sub> ,<br>PV <sub>DD</sub> | $AV_{DD} = PV_{DD}$                           |                  | 1.8  |      | 3.6  | V     |

| Digital Supply Voltage              | DV <sub>DD</sub>                       |                                               |                  | 1.8  |      | 3.6  | V     |

|                                     |                                        | Full operation (Note 2), no headphone or line | $AV_{DD} = 1.8V$ |      | 5.5  | 7.7  |       |

| Analog Supply Current               | AIDD                                   | output load                                   | $AV_{DD} = 3.0V$ |      | 5.9  |      | mA    |

|                                     |                                        | Full operation (Note 2),                      | $AV_{DD} = 1.8V$ |      | 3.5  | 5.3  |       |

|                                     |                                        | headphones disabled                           | $AV_{DD} = 3.0V$ |      | 3.75 |      |       |

| Digital Supply Current              | DIDD                                   | Full operation (Note 2),                      | $DV_{DD} = 1.8V$ |      | 2.1  | 2.9  | mA    |

| Digital Supply Current              | טטוט                                   | no line output load                           | $DV_{DD} = 3.0V$ |      | 3.8  |      | ША    |

| Analog Shutdown Current             | AISHDN                                 | IAVDD + IPVDD, AVDD = PVDD = 1.8V             |                  |      | 1.5  | 10   | μA    |

| Digital Shutdown Current            | DISHDN                                 | Static digital interface, D                   | /DD = 1.8V       |      | 0.3  | 5    | μA    |

| Shutdown to Full Operation (Note 2) | t <sub>ON</sub>                        |                                               |                  |      | 1.3  |      | ms    |

| Power-On to Full Operation (Note 2) | <sup>t</sup> PON                       |                                               |                  |      | 1.4  |      | ms    |

| DAC PERFORMANCE/LINE O              | JTPUTS (Note 3                         | 3)                                            |                  |      |      |      |       |

| 0dBFS Output Voltage                | Vout_fs                                |                                               |                  | 1.85 | 1.95 | 2.05 | VP-P  |

| Dynamia Danga (Nota 4)              | DR                                     | $AV_{DD} = 3.0V$                              |                  |      | 87.5 |      | dB    |

| Dynamic Range (Note 4)              | DR                                     | $AV_{DD} = 1.8V$                              |                  | 82   | 87.5 |      | uБ    |

|                                     |                                        | Unweighted                                    |                  |      | 88   |      |       |

| Signal-to-Noise Ratio               | SNR                                    | A-weighted                                    |                  |      | 91   |      | dD    |

| (Note 5)                            | SINK                                   | AV <sub>DD</sub> = 1.8V, unweighted           | k                |      | 88   |      | dB    |

|                                     |                                        | AV <sub>DD</sub> = 1.8V, A-weighted           | k l              |      | 91   |      |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = AV_{DD} = PV_{DD} = 3.0V, AGND = DGND = PGND = 0V, C1 = 0.47\mu$ F, C2 = 2.2 $\mu$ F, C<sub>NREG</sub> = C<sub>PREG</sub> = C<sub>REF</sub> = 1 $\mu$ F to AGND, R<sub>LOAD\_HP</sub> = 32 $\Omega$  to AGND, R<sub>LOAD\_OUT</sub> = 10 $k\Omega$  to AGND, f<sub>LRCLK</sub> = 48kHz, f<sub>MCLK</sub> = 12.288MHz, volume set to -9.5dB, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical specifications at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                               | SYMBOL               | CONDITIONS                                                                         |                                     | MIN                      | ТҮР   | МАХ                      | UNITS |

|-----------------------------------------|----------------------|------------------------------------------------------------------------------------|-------------------------------------|--------------------------|-------|--------------------------|-------|

|                                         |                      |                                                                                    | 0dBFS                               |                          | 87    |                          |       |

|                                         |                      | f <sub>IN</sub> = 984.375Hz                                                        | -60dBFS                             |                          | 27.5  |                          |       |

| Total Harmonic Distortion Plus<br>Noise | THD+N                |                                                                                    | AV <sub>DD</sub> = 1.8V,<br>0dBFS   |                          | -81   |                          | dB    |

|                                         |                      |                                                                                    | AV <sub>DD</sub> = 1.8V,<br>-60dBFS |                          | -27.5 | -22                      |       |

| Line Output Offset Voltage              | V <sub>OS_LINE</sub> |                                                                                    |                                     | -15                      | 0     | +15                      | mV    |

| Channel-to-Channel Gain<br>Matching     | ΔAV/AV               | OUTL to OUTR, OUTF                                                                 | R to OUTL                           |                          | ±0.04 |                          | dB    |

|                                         | DODD                 | $V_{RIPPLE} = 100mV_{P-P},$<br>AV_DD and PV_DD                                     | f <sub>IN</sub> = 1kHz, applied to  |                          | 87    |                          | Ē     |

| Power-Supply Rejection Ratio            | PSRR                 | $V_{RIPPLE} = 100mV_{P-P}$ , $f_{IN} = 20kHz$ , applied to $AV_{DD}$ and $PV_{DD}$ |                                     | 67                       |       | – dB                     |       |

| Crosstalk                               | XTALK                | $f_{OUT} = 1$ kHz, $V_{OUT} = 2V_{P-P}$<br>(OUTL to OUTR) or (OUTR to OUTL)        |                                     |                          | -105  |                          | dB    |

| Sampling Frequency Range                | fs                   |                                                                                    |                                     | 8                        |       | 48                       | kHz   |

| MCLK Frequency                          | fMCLK                |                                                                                    |                                     | 8.448                    |       | 40                       | MHz   |

| DAC 8x INTERPOLATION FILTE              | ER                   |                                                                                    |                                     |                          |       |                          |       |

| Passband Frequency                      | PB                   | To -1dB corner                                                                     |                                     | 0                        |       | 0.48 x<br>f <sub>S</sub> | kHz   |

| Frequency Response                      | FR                   | 10Hz to 20kHz                                                                      |                                     | -0.1                     |       | +0.1                     | dB    |

| Stopband Attenuation                    | SBA                  |                                                                                    |                                     | 58                       |       |                          | dB    |

| Stopband Frequency                      | SB                   | Attenuation greater th                                                             | an SBA                              | 0.58 x<br>f <sub>S</sub> |       | 7.42 x<br>f <sub>S</sub> | kHz   |

| LINE INPUTS (INL, INR)                  |                      | ·                                                                                  |                                     |                          |       |                          |       |

| Line Input Voltage                      | VIN_LINE             |                                                                                    |                                     | -1                       |       | +1                       | V     |

| IN_ to OUT_ Gain                        | Av_LINE              |                                                                                    |                                     | -1.05                    | -1    | -0.95                    | V/V   |

| Line Input Bias Voltage                 | VBIAS_LINE           |                                                                                    |                                     | -15                      | 0     | +15                      | mV    |

| INL and INR Input Resistance            | RIN_LINE             |                                                                                    |                                     | 10                       | 22    |                          | kΩ    |

| INTERNAL REGULATORS (NR                 | EG, PREG)            |                                                                                    |                                     |                          |       |                          |       |

| PREG Output Voltage                     | VPREG                |                                                                                    |                                     |                          | 1.60  |                          | V     |

| NREG Output Voltage                     | VNREG                |                                                                                    |                                     |                          | -1.15 |                          | V     |

| REF Output Voltage                      | VREF                 |                                                                                    |                                     |                          | 1.23  |                          | V     |

# **MAX9850**

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = AV_{DD} = PV_{DD} = 3.0V, AGND = DGND = PGND = 0V, C1 = 0.47\mu$ F, C2 = 2.2 $\mu$ F, C<sub>NREG</sub> = C<sub>PREG</sub> = C<sub>REF</sub> = 1 $\mu$ F to AGND, R<sub>LOAD\_HP</sub> = 32 $\Omega$  to AGND, R<sub>LOAD\_OUT</sub> = 10k $\Omega$  to AGND, f<sub>LRCLK</sub> = 48kHz, f<sub>MCLK</sub> = 12.288MHz, volume set to -9.5dB, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical specifications at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                        | SYMBOL  | CONDITIONS                                                                                 |                                     | MIN   | ТҮР   | МАХ  | UNITS            |  |

|--------------------------------------------------|---------|--------------------------------------------------------------------------------------------|-------------------------------------|-------|-------|------|------------------|--|

| HEADPHONE OUTPUTS (HPL, H                        | PR)     |                                                                                            |                                     | •     |       |      |                  |  |

|                                                  |         |                                                                                            | $R_{L} = 16\Omega$ $AV_{DD} = 3.0V$ |       | 95    |      |                  |  |

|                                                  |         | THD+N = 1%                                                                                 | $R_{L} = 32\Omega$ $AV_{DD} = 3.0V$ | 40    | 65    |      |                  |  |

| Output Power                                     | OUT     | $f_{IN} = 1 kHz$ , headphone<br>volume = +6dB                                              | $R_{L} = 16\Omega$ $AV_{DD} = 1.8V$ |       | 30    |      | mW               |  |

|                                                  |         |                                                                                            | $R_{L} = 32\Omega$ $AV_{DD} = 1.8V$ | 15    | 25    |      |                  |  |

| Full-Scale Headphone Amplifier<br>Output Voltage | Vout_fs | Volume = +5dB, HP unlo                                                                     | baded                               | 1.16  | 1.23  | 1.30 | V <sub>RMS</sub> |  |

| Line In to HP Output Voltage<br>Gain             | Av_hp   | Volume = +3dB, HP unlo                                                                     | baded                               | 1.34  | 1.41  | 1.48 | V/V              |  |

| Total Harmonic Distortion Plus                   | THD+N   | $R_L = 32\Omega$ , $P_{OUT} = 60mV$                                                        | /, f <sub>IN</sub> = 1kHz           |       | -94   |      | dB               |  |

| Noise                                            |         | $R_L = 16\Omega, P_{OUT} = 60 \text{mW}$                                                   | /, f <sub>IN</sub> = 1kHz           |       | -90   |      | UD               |  |

| Signal-to-Noise Ratio (Note 6)                   |         | SNR Unweighted A-weighted A-weighted AVDD = 1.8V, unweighted                               |                                     |       | 88    |      |                  |  |

|                                                  |         |                                                                                            |                                     |       | 90    |      |                  |  |

|                                                  | SINK    |                                                                                            |                                     |       | 88    | dB   |                  |  |

|                                                  |         | AV <sub>DD</sub> = 1.8V, A-weighte                                                         |                                     | 91    |       |      |                  |  |

|                                                  | 2022    | $V_{RIPPLE} = 100 MV_{P-P}$ , frequency = 1kHz,<br>applied to AV_DD and PV_DD              |                                     |       | 91    |      |                  |  |

| Power-Supply Rejection Ratio                     | PSRR    | $V_{RIPPLE} = 100mV_{P-P}$ , fre applied to $AV_{DD}$ and $PV_{DD}$                        |                                     |       | 72    |      | dB               |  |

| Headphone Output Offset                          |         | Т. Т.                                                                                      | A = +25°C                           | -15   |       | +15  |                  |  |

| Voltage                                          | VOS_HP  | Volume = -11.5dB                                                                           | $A = T_{MIN}$ to $T_{MAX}$          | -25   |       | +25  | mV               |  |

| Slew Rate                                        | SR      |                                                                                            |                                     |       | 0.47  |      | V/µs             |  |

| Maximum Capacitive Load                          | CL      | No sustained oscillations                                                                  | 3                                   |       | 150   |      | pF               |  |

| Crosstalk                                        | XTALK   | $R_{HP} = 32\Omega$ , $P_{OUT} = 3.5$ mW, $f_{IN} = 1$ kHz<br>(HPL to HPR) or (HPR to HPL) |                                     |       | -85   |      | dB               |  |

| Channel-to-Channel Gain<br>Matching              | ΔΑγ/Αγ  |                                                                                            |                                     |       | ±0.05 |      | dB               |  |

| Internal Charge-Pump Oscillator<br>Frequency     | fCP     |                                                                                            |                                     | 550   | 667   | 775  | kHz              |  |

| Charge-Pump Operating<br>Frequency Range         |         | Charge-pump clock deri                                                                     | ved from MCLK                       | 550   |       | 775  | kHz              |  |

| Volume Control Range                             |         |                                                                                            |                                     | -73.5 |       | +6.0 | dB               |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = AV_{DD} = PV_{DD} = 3.0V, AGND = DGND = PGND = 0V, C1 = 0.47\mu$ F, C2 = 2.2 $\mu$ F, C<sub>NREG</sub> = C<sub>PREG</sub> = C<sub>REF</sub> = 1 $\mu$ F to AGND, R<sub>LOAD\_HP</sub> = 32 $\Omega$  to AGND, R<sub>LOAD\_OUT</sub> = 10 $k\Omega$  to AGND, f<sub>LRCLK</sub> = 48kHz, f<sub>MCLK</sub> = 12.288MHz, volume set to -9.5dB, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical specifications at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                        | SYMBOL                            | CONDITIO                                           | ONS            | MIN                       | ТҮР                        | МАХ                        | UNITS |

|----------------------------------|-----------------------------------|----------------------------------------------------|----------------|---------------------------|----------------------------|----------------------------|-------|

| Mute Attenuation                 |                                   |                                                    |                |                           | 100                        |                            | dB    |

| DIGITAL INPUTS (GPIO, SCL, S     | DA, BCLK, LF                      | CLK, SDIN, ADD, MCLK)                              |                |                           |                            |                            |       |

| Input High Voltage               | VIH                               |                                                    |                | 0.8 x<br>DV <sub>DD</sub> |                            |                            | V     |

| Input Low Voltage                | VIL                               |                                                    |                |                           |                            | 0.2 x<br>DV <sub>DD</sub>  | V     |

| Input Leakage Current            | I <sub>IH</sub> , I <sub>IL</sub> | $V_{IH} = DV_{DD}, V_{IL} = DGND$                  | )              | -10                       |                            | +10                        | μA    |

| Input Hysteresis                 |                                   |                                                    |                |                           | 0.09 x<br>DV <sub>DD</sub> |                            | V     |

| Input Capacitance                | CIN                               |                                                    |                |                           | 10                         |                            | pF    |

| <b>OPEN-DRAIN DIGITAL OUTPUT</b> | 'S (GPIO, SDA                     | A)                                                 |                |                           |                            |                            |       |

| Output-High Leakage Current      | IOH                               | $V_{OH} = DV_{DD}$ (Note 7)                        |                |                           |                            | 1                          | μA    |

| Output Low Voltage V             |                                   | $I_{OL} = 3mA$<br>$DV_{DD} > 2V$<br>$DV_{DD} < 2V$ | $DV_{DD} > 2V$ |                           |                            | 0.4                        | V     |

|                                  | V <sub>OL</sub>                   |                                                    | $DV_{DD} < 2V$ |                           |                            | 0.2 x<br>DV <sub>DD</sub>  |       |

| CMOS DIGITAL OUTPUTS (BCL        | .K, LRCLK)                        |                                                    |                |                           |                            |                            | -     |

| Output High Voltage              | V <sub>OH</sub>                   | I <sub>OH</sub> = 1mA                              |                | DV <sub>DD</sub> -<br>0.4 |                            |                            | V     |

| Output Low Voltage               | Vol                               | I <sub>OL</sub> = 1mA                              |                |                           |                            | 0.4                        | V     |

| HEADPHONE SENSE INPUT (H         | PS)                               |                                                    |                |                           |                            |                            |       |

| Input High Voltage               | VIH                               |                                                    |                | 0.7 x<br>DV <sub>DD</sub> |                            |                            | V     |

| Input Low Voltage                | VIL                               |                                                    |                |                           |                            | 0.25 x<br>DV <sub>DD</sub> | V     |

| Input-High Leakage Current       | Lu .                              | Full shutdown, $V_{IH} = DV_D$                     | D              |                           |                            | 400                        |       |

| Input-High Leakage Current       | Ιн                                | Normal operation, $V_{IH} = DV_{DD}$               |                |                           |                            | 1                          | μA    |

| Input-Low Leakage Current        | ١ <sub>١L</sub>                   | Full shutdown, VIL = DGN                           | 1D             |                           |                            | 1                          | μA    |

|                                  | ΠL                                | Normal operation, $V_{IL} = D$                     | DGND           |                           |                            | 100                        | μΛ    |

| Input Hysteresis                 |                                   |                                                    |                |                           | 0.05 x<br>DV <sub>DD</sub> |                            | V     |

#### TIMING CHARACTERISTICS

$(DV_{DD} = AV_{DD} = PV_{DD} = 3.0V, AGND = DGND = PGND = 0V, C1 = 0.47\mu$ F, C2 = 2.2 $\mu$ F, C<sub>NREG</sub> = C<sub>PREG</sub> = C<sub>REF</sub> = 1 $\mu$ F to AGND, R<sub>LOAD</sub>\_HP = 32 $\Omega$  to AGND, R<sub>LOAD</sub>\_LINE = 10 $k\Omega$  to AGND, f<sub>LRCLK</sub> = 48kHz, f<sub>MCLK</sub> = 12.288MHz, volume set to -9.5dB, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical specifications at T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                       | SYMBOL                     | CONDITIONS                                      | MIN TYP                      | МАХ    | UNITS |

|-------------------------------------------------|----------------------------|-------------------------------------------------|------------------------------|--------|-------|

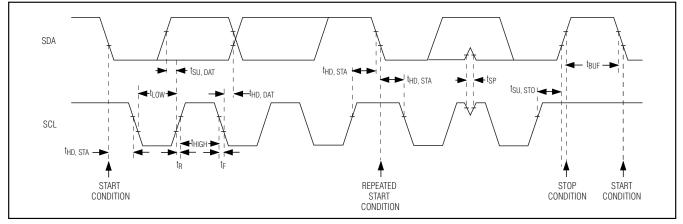

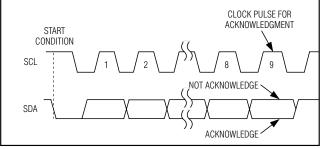

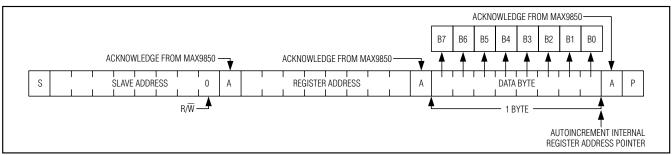

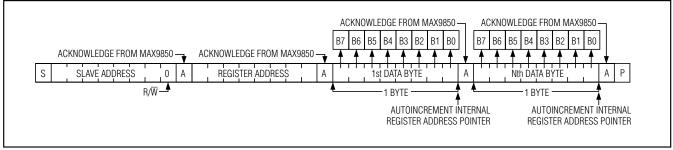

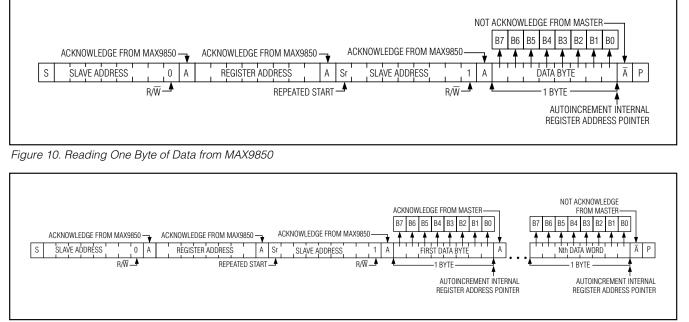

| I <sup>2</sup> C TIMING                         |                            | •                                               |                              |        |       |

| Serial Clock Frequency                          | fscl                       |                                                 | 0                            | 400    | kHz   |

| Bus Free Time Between STOP and START Conditions | tBUF                       |                                                 | 1.3                          |        | μs    |

| Hold Time (Repeated) START<br>Condition         | <sup>t</sup> HD, STA       |                                                 | 0.6                          |        | μs    |

| SCL Pulse-Width Low                             | tLOW                       |                                                 | 1.3                          |        | μs    |

| SCL Pulse-Width High                            | thigh                      |                                                 | 0.6                          |        | μs    |

| Repeated START Condition<br>Setup Time          | <sup>t</sup> SU, STA       |                                                 | 0.6                          |        | μs    |

| Data Hold Time                                  | thd, dat                   |                                                 | 0                            | 900    | ns    |

| Data Setup Time                                 | tsu, dat                   |                                                 | 100                          |        | ns    |

| Bus Capacitance                                 | CB                         |                                                 |                              | 400    | pF    |

| SDA and SCL Receiving Rise<br>Time (Note 8)     | t <sub>R</sub>             |                                                 | 20 +<br>0.1C <sub>B</sub>    | 300    | ns    |

| SDA and SCL Receiving Fall<br>Time (Note 8)     | tF                         |                                                 | 20 +<br>0.1C <sub>B</sub>    | 300    | ns    |

| SDA Transmitting Fall Time                      | +_                         | DV <sub>DD</sub> = 1.8V, T <sub>A</sub> = +25°C | 20 +<br>0.1C <sub>B</sub>    | 250    |       |

| (Note 8)                                        | tF                         | DV <sub>DD</sub> = 3.6V, T <sub>A</sub> = +25°C | 20 +<br>0.05C <sub>B</sub>   | 250    | ns    |

| Setup Time for STOP Condition                   | tsu, sto                   |                                                 | 0.6                          |        | μs    |

| Pulse Width of Suppressed Spike                 | t <sub>SP</sub>            |                                                 | 0                            | 50     | ns    |

| DIGITAL AUDIO TIMING                            |                            |                                                 |                              |        |       |

| BCLK Period (Note 9)                            | <sup>t</sup> BCLK          |                                                 | 3 x<br>1 / f <sub>ICLK</sub> |        | ns    |

| Low or High BCLK Pulse Width                    | <sup>t</sup> BCLK_PW       |                                                 | 0.35 x<br>tBCLK              |        | ns    |

| BCLK and LRCLK Rise Time                        | t <sub>R</sub>             | Master mode, $C_{LOAD} = 15 pF$                 | 1                            |        | ns    |

| BCLK and LRCLK Fall Time                        | t⊨                         | Master mode, $C_{LOAD} = 15 pF$                 | 1                            |        | ns    |

| SDIN or LRCLK to BCLK Rising<br>Setup Time      | tdbsu,<br>tbwsu            |                                                 | 30                           |        | ns    |

| SDIN or LRCLK to BCLK Rising<br>Hold Time       | t <sub>DBH,</sub><br>tвwвн | $DV_{DD} = 1.8V$ $DV_{DD} = 3.6V$               |                              | 0<br>5 | ns    |

Note 1: The MAX9850 is 100% production tested at  $T_A = +25^{\circ}C$  and is guaranteed by design for  $T_A = T_{MIN}$  to  $T_{MAX}$ .

**Note 2:** Full operation is defined as clocking all zeros into the DAC while the DAC, headphone outputs, and line outputs are all enabled. **Note 3:** DAC performance specifications measured using the line outputs, OUTL and OUTR.

Note 4: Dynamic range is defined as the SNR of a 1kHz, -60dBFS input signal measured with an A-weighted filter, then normalized to full scale (+60dB).

**Note 5:** DAC SNR measured from DAC inputs to OUTL and OUTR.

Note 6: Headphone amplifier SNR measured from line inputs to headphone outputs.

Note 7: GPIO is  $100k\Omega$  to ground when  $DV_{DD} < V_{OH} < 3.6V$ .

Note 8: CB is in pF.

Note 9: f<sub>ICLK</sub> derived by dividing f<sub>MCLK</sub> by 1, 2, 3, or 4. See the *Registers and Bit Descriptions* section.

#### TYPICAL POWER DISSIPATION AT AVDD = 1.8V (No Headphone/Line Output Load)

| MODE                                                               | AV <sub>DD</sub> POWER | DV <sub>DD</sub> POWER | PV <sub>DD</sub> POWER | TOTAL POWER |

|--------------------------------------------------------------------|------------------------|------------------------|------------------------|-------------|

| Full Operation (Note 1)                                            | 4.93mW                 | 3.76mW                 | 5.00mW                 | 13.70mW     |

| DAC to Line Outputs, Headphones Disabled                           | 3.11mW                 | 3.76mW                 | 3.22mW                 | 10.10mW     |

| Line Inputs to Line Outputs and Headphone<br>Outputs, DAC Disabled | 3.22mW                 | 0.085mW                | 3.40mW                 | 6.71mW      |

| Line Inputs to Line Outputs, DAC and Headphones Disabled           | 1.39mW                 | 0.085mW                | 1.61mW                 | 3.08mW      |

| Full Shutdown                                                      | 2.7µW                  | 0.5µW                  | <0.1µW                 | 3.2µW       |

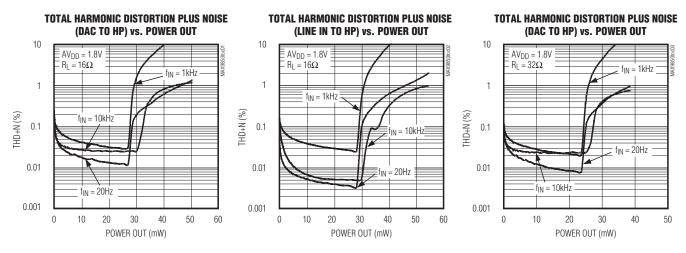

#### **Typical Operating Characteristics**

$(DV_{DD} = AV_{DD} = PV_{DD} = 3.0V, AGND = DGND = PGND = 0V, C1 = 0.47\mu$ F, C2 = 2.2 $\mu$ F, C<sub>NREG</sub> = C<sub>PREG</sub> = C<sub>REF</sub> = 1 $\mu$ F, f<sub>S</sub> = 48kHz, f<sub>MCLK</sub> = 12.288MHz, master integer mode, headphone volume set to +6dB, both channels driven in-phase, T<sub>A</sub> = +25°C, unless otherwise noted. f<sub>IN</sub> = 984.375Hz, A-weighted THD+N.)

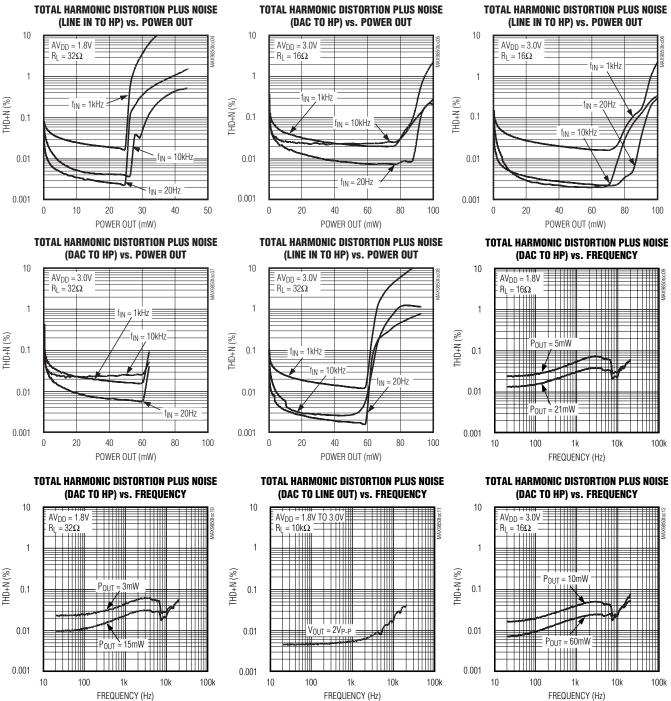

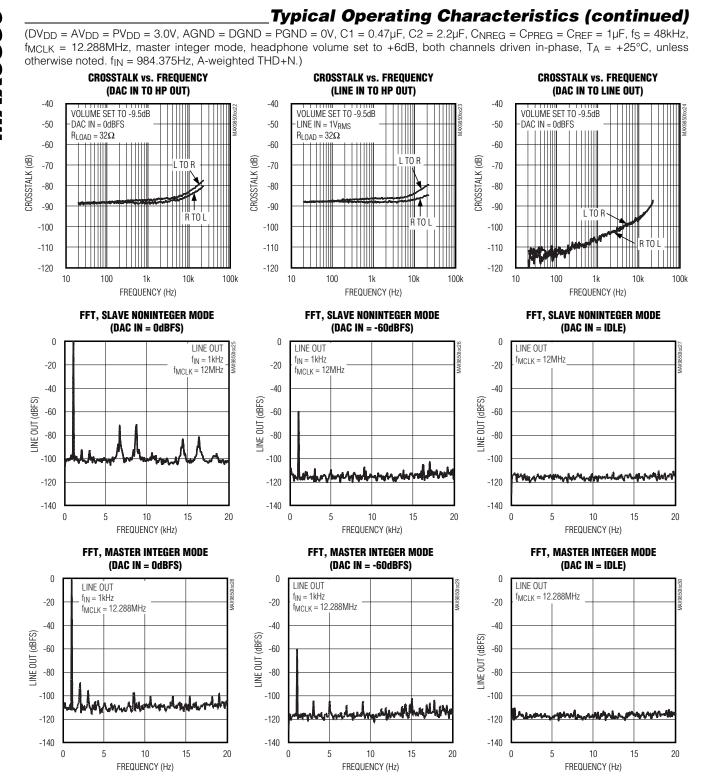

#### **Typical Operating Characteristics (continued)**

(DV<sub>DD</sub> = AV<sub>DD</sub> = PV<sub>DD</sub> = 3.0V, AGND = DGND = PGND = 0V, C1 = 0.47µF, C2 = 2.2µF, C<sub>NREG</sub> = C<sub>PREG</sub> = C<sub>REF</sub> = 1µF, fs = 48kHz, MCLK = 12.288MHz, master integer mode, headphone volume set to +6dB, both channels driven in-phase, TA = +25°C, unless otherwise noted.  $f_{IN} = 984.375$ Hz, A-weighted THD+N.)

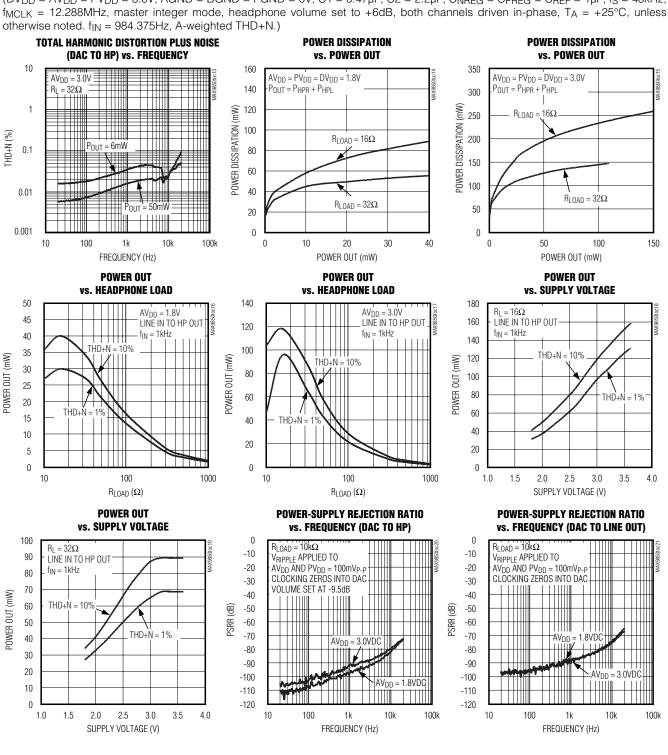

#### Typical Operating Characteristics (continued)

(DVDD = AVDD = PVDD = 3.0V, AGND = DGND = PGND = 0V, C1 = 0.47µF, C2 = 2.2µF, CNREG = CPREG = CREF = 1µF, fS = 48kHz,

**MAX9850**

/N/IXI/N

**MAX9850**

10

#### MCLK = 12.288MHz, master integer mode, headphone volume set to +6dB, both channels driven in-phase, TA = +25°C, unless GAIN FLATNESS WIDEBAND FFT **SNR vs. MCLK FREQUENCY** vs. FREOUENCY 20 1.0 100 DAC IN = 0dBFS $R_{IOAD} = 32\Omega$ fICLK = fMCLK / 1 ficik = fmcik/3 0.8 0 DAC IN TO LINE OUT DAC IN TO HP 95 $f_{IN} = 1 kHz$ DAC IN = 0dBFS 0.6 -20 90 0.4 -40 85 0.2 V<sub>0UT</sub> (dBFS) (gB) fICLK = fMCLK / 2 fICLK = fMCLK / SNR (dB) -60 0 GAIN 80 -0.2 -80 75 -0.4 -100 70 SLAVE NONINTEGER MODE -0.6 DAC IN = -60dBFS -120 65 -0.8 fLRCLK = 32kHz, 44.1kHz, 48kHz $AV_{DD} = 3.0V$ -140 60 -1.0 10 100 1k 10k 100k 10 100 1k 10k 100k 5 10 20 35 40 15 25 30 FREQUENCY (Hz) FREQUENCY (Hz) MCLK FREQUENCY (MHz) **OUTPUT POWER** vs. TEMPERATURE WIDEBAND FFT 20 40 DAC IN = -60dBFS $AV_{DD} = 1.8V$ DAC IN TO LINE OUT 0 THD+N = 1% 35 f<sub>IN</sub> = 1kHz $R_{LOAD}=16\Omega$ -20 OUTPUT POWER (mW) 30 -40 V<sub>0UT</sub> (dBFS) $R_{LOAD} = 32\Omega$ -60 25 -80 20 -100 15 -120 i Tillar -140 10 10 100 10k 100k -40 -15 10 35 60 85 1k FREQUENCY (Hz) TEMPERATURE (°C) AVDD AND PVDD SUPPLY CURRENT **DIGITAL SUPPLY CURRENT** vs. AVDD AND PVDD SUPPLY VOLTAGE vs. DV<sub>DD</sub> 10 10 9 9 AVDD + PVDD SUPPLY CURRENT (mA) DIGITAL SUPPLY CURRENT (mA) 8 8 T<sub>A</sub> = +85°C 7 7 6 5 6 $T_A = +85^{\circ}C, +25^{\circ}C, -40^{\circ}C$ 4 5 3 4 T<sub>A</sub> = -40°C $T_A = +25^{\circ}C$ 2 3 1 2 0 1.8 2.0 2.2 2.4 2.6 2.8 3.0 3.2 3.4 3.6 1.5 2.0 2.5 1.0 3.0 3.5 4.0

#### Typical Operating Characteristics (continued)

DV<sub>DD</sub> (V)

(DVDD = AVDD = PVDD = 3.0V, AGND = DGND = PGND = 0V, C1 = 0.47µF, C2 = 2.2µF, CNREG = CPREG = CREF = 1µF, fS = 48kHz, otherwise noted. f<sub>IN</sub> = 984.375Hz, A-weighted THD+N.)

M/X/M

AV<sub>DD</sub> AND PV<sub>DD</sub> (V)

MAX9850

**Pin Description**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                       |

|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | LRCLK            | Digital Audio Left-Right Clock Input/Output. LRCLK is the audio sample rate clock and determines whether the audio data on SDIN is routed to the left or right channel. LRCLK is an input when the MAX9850 is in slave mode and an output when in master mode. |

| 2   | BCLK             | Digital Audio Bit Clock Input/Output. BCLK is an input when the MAX9850 is in slave mode and an output when in master mode.                                                                                                                                    |

| 3   | SDIN             | Digital Audio Serial Data Input                                                                                                                                                                                                                                |

| 4   | DV <sub>DD</sub> | Digital Power-Supply Input. Bypass to DGND with a 1µF ceramic capacitor.                                                                                                                                                                                       |

| 5   | MCLK             | Master Clock Input. All internal digital clocks are derived from MCLK.                                                                                                                                                                                         |

| 6   | DGND             | Digital Ground                                                                                                                                                                                                                                                 |

| 7   | ADD              | I <sup>2</sup> C Address-Select Input. Connect to AGND, AV <sub>DD</sub> , or SDA to select one of the three possible I <sup>2</sup> C addresses.                                                                                                              |

| 8   | GPIO             | General-Purpose Input/Output. Configure GPIO as an input or an output through the GPIO register. GPIO can perform the function of an interrupt when configured as an output. See the <i>GPIO</i> section.                                                      |

| 9   | INR              | Right-Channel Line Input. INR is mixed with the right DAC output.                                                                                                                                                                                              |

| 10  | INL              | Left-Channel Line Input. INL is mixed with the left DAC output.                                                                                                                                                                                                |

| 11  | OUTR             | Line Level Right-Channel Output. OUTR is biased at AGND.                                                                                                                                                                                                       |

| 12  | OUTL             | Line Level Left-Channel Output. OUTL is biased at AGND.                                                                                                                                                                                                        |

| 13  | REF              | Reference Output. Bypass to AGND with a 1µF ceramic capacitor.                                                                                                                                                                                                 |

| 14  | AGND             | Analog Ground                                                                                                                                                                                                                                                  |

| 15  | NREG             | Line Output Negative Regulator Output. Bypass to AGND with a 1µF capacitor.                                                                                                                                                                                    |

| 16  | PREG             | Line Output Positive Regulator Output. Bypass to AGND with a 1µF capacitor.                                                                                                                                                                                    |

| 17  | AV <sub>DD</sub> | Analog Power Supply. Bypass to AGND with a 1µF ceramic capacitor.                                                                                                                                                                                              |

| 18  | HPR              | Right-Channel Headphone Output. HPR is a DirectDrive output biased at AGND.                                                                                                                                                                                    |

| 19  | HPL              | Left-Channel Headphone Output. HPL is a DirectDrive output biased at AGND.                                                                                                                                                                                     |

| 20  | SVSS             | Headphone Amplifier Negative Power-Supply Input. Connect to PVSS.                                                                                                                                                                                              |

| 21  | HPS              | Headphone Sense Input. Connect to the control pin of a headphone jack for automatic headphone sensing. Float HPS if unused. See the <i>Headphone Sense Input (HPS)</i> section.                                                                                |

| 22  | PV <sub>SS</sub> | Inverting Charge-Pump Output. Bypass to PGND with a $2.2\mu$ F ceramic capacitor and connect to SV <sub>SS</sub> to provide the headphone amplifiers with a negative supply.                                                                                   |

| 23  | C1N              | Charge-Pump Flying Capacitor Negative Terminal. Connect a 0.47µF ceramic capacitor between C1N and C1P.                                                                                                                                                        |

| 24  | PGND             | Charge-Pump Ground                                                                                                                                                                                                                                             |

| 25  | C1P              | Charge-Pump Flying Capacitor Positive Terminal. Connect a 0.47µF ceramic capacitor between C1P and C1N.                                                                                                                                                        |

| 26  | PV <sub>DD</sub> | Charge-Pump and Headphone Amplifier Positive Power-Supply Input. Bypass to PGND with a $1\mu F$ ceramic capacitor. Connect to AV_DD for normal operation.                                                                                                      |

| 27  | SCL              | I <sup>2</sup> C-Compatible Serial Clock Input                                                                                                                                                                                                                 |

| 28  | SDA              | I <sup>2</sup> C-Compatible Serial Data Input/Output                                                                                                                                                                                                           |

| _   | EP               | Exposed Thermal Pad. Connect EP to AGND.                                                                                                                                                                                                                       |

Functional Diagram/Typical Operating Circuit

MAX9850

#### **Detailed Description**

The MAX9850 audio digital-to-analog converter (DAC) with a stereo DirectDrive headphone amplifier is a complete digital audio playback solution. The sigma-delta DAC has 90dB of dynamic range and accepts stereo audio data at sampling frequencies ranging from 8kHz to 48kHz. Headphone output volume level, muting, and device configuration are programmed through the I<sup>2</sup>C-compatible interface. Three selectable I<sup>2</sup>C device IDs are available. Both basic modes of operation, integer and noninteger, provide full dynamic range performance and allow maximum flexibility when choosing the MAX9850's master clock (MCLK) frequency. Integer mode operation requires that MCLK is an integer multiple of 16 times the sample rate, and provides maximum full-scale SNR performance. Noninteger mode allows maximum flexibility when choosing an MCLK frequency, as the MCLK may be any frequency in the acceptable range.

Audio data is sent to the MAX9850 through a 3-wire digital audio data bus that supports numerous input formats. LRCLK and BCLK signals are generated by the MAX9850 when configured in master mode. The MAX9850 can also be configured as a slave device, accepting LRCLK and BCLK signals from an external digital audio master. External LRCLK and BCLK signals may be either synchronous or asynchronous with MCLK when the MAX9850 is configured as a slave device.

Maxim's DirectDrive architecture employs an internal charge pump to create a negative voltage supply to power the headphone amplifier outputs. The internal negative supply allows the analog output signals to be biased at ground, eliminating the need for an outputcoupling capacitor, reducing system cost and size.

The MAX9850's stereo line inputs allow mixing of analog audio with digital audio. The summed audio signal is sent directly to the line and headphone outputs. The line inputs/outputs can be activated even when the DAC is disabled and MCLK is not present.

The headphone sense input (HPS) detects when a headphone is connected to the MAX9850. The HPS circuit shuts down the headphone amplifier outputs when no headphones are connected. The headphone amplifiers can be automatically enabled when HPS detects the presence of headphones.

#### Sigma-Delta DAC

The MAX9850 uses a sigma-delta DAC to achieve up to 91dB of SNR. The DAC receives a stereo digital input signal sampled at  $f_{LRCLK}$ , interpolates the signal data to an 8 times  $f_{LRCLK}$  frequency, and digitally filters the

samples. The resulting oversampled digital signal is then converted using a multibit sigma-delta modulator followed by an analog smoothing filter that greatly attenuates high-frequency quantization noise typical with oversampling converters. Flexible clocking modes allow the MAX9850 to be used effectively in applications normally not well suited for oversampling converters all without the need for expensive sample rate converters.

Set DACEN = 0 in the enable register (register 0x5, bit B0) to disable the DAC. Set DACEN = 1 to enable the DAC.

#### Line Outputs/Inputs

The MAX9850 features line inputs (INR, INL) and line outputs (OUTR, OUTL). The line inputs allow a line level signal to be mixed with the DAC output, see the *Functional Diagram/Typical Operating Circuit*. Set LNIEN = 1 in the enable register (register 0x5, bit B1) to enable the line inputs. The line inputs are biased at AGND and can be directly coupled or AC-coupled to INR and INL, depending on the signal source.

Stereo DirectDrive line outputs (OUTR and OUTL) can be used to drive line-level loads. Line outputs internally drive the inputs of the headphone amplifier. Set LNOEN = 1 in the enable register (register 0x5, bit B2) to enable the line outputs. Disabling the line outputs will also disable the headphone outputs.

The internal charge pump must be enabled to operate the line outputs. Enable the charge pump by configuring CPEN(1:0) = 11 in the enable register (register 0x5, bit B5 and B4). See the *Charge Pump* section.

#### DirectDrive Headphone and Line Amplifiers

Unlike the MAX9850, traditional single-supply headphone amplifiers have their outputs biased about a nominal DC voltage, typically half the supply, for maximum dynamic range. Large coupling capacitors are typically needed to block this DC bias from the headphone. Without these capacitors, a significant amount of DC current flows to the headphone, resulting in unnecessary power dissipation and possible damage to both headphone and headphone amplifier.

Maxim's patented DirectDrive architecture uses a charge pump to create an internal negative supply voltage. This allows the MAX9850 headphone and line outputs to be biased about ground, almost doubling the dynamic range while operating from a single supply. With no DC component, there is no need for the large DC-blocking capacitors. Instead of two large ( $33\mu$ F to  $330\mu$ F) capacitors, the MAX9850 charge pump

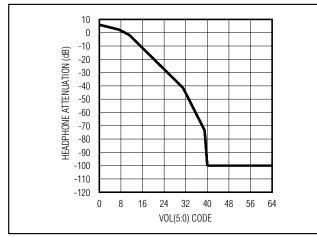

Figure 1. Headphone Amplifier Attenuation Profile

requires only two small ceramic capacitors (0.47µF and 2.2µF), conserving board space, reducing cost, improving the frequency response, and THD of the headphone amplifier. In addition to the cost and size disadvantages, the DC-blocking capacitors required by conventional headphone amplifiers limit low-frequency response and decrease PSRR performance. Some dielectrics can significantly distort the audio signal.

#### Volume Control

Program VOL(5:0) in the volume register (register 0x2, bits B5–B0) to set the volume attenuation of the headphone amplifiers. Program VOL(5:0) to 0x00 for full volume. Minimum volume occurs at VOL(5:0) greater than or equal to 0x28. VMN in the status A register (register 0x0, bit B3) sets to 1 when the MAX9850 output is programmed to and reaches volume step 0x3F. Figure 1 shows the attenuation profile for each VOL(5:0) value.

Volume Slew, Zero-Crossing Detect, and Mute

Set SLEW = 1 in the volume register (register 0x2, bit B6) to enable the volume slew circuit. When SLEW = 1 headphone amplifier volume changes will slew between programmed levels smoothly. Set the volume slew rate with SR(1:0) in the charge-pump register (register 0x7, bits B7 and B6). Table 1 lists the volume slew-rate settings for each value of SR(1:0).

Set ZDEN = 1 in the general-purpose register (register 0x3, bit B0) to force volume changes and headphone amplifier muting to occur when the audio signal is at its zero crossing. For optimal performance, set SR(1:0) to 01. This zero-crossing detection reduces audible clicks/pops caused when transitioning or slewing between volume levels.

#### Table 1. Slew-Rate Settings

|     |     | TYPICAL VOLUME SLEW RATE    |                                        |  |  |  |

|-----|-----|-----------------------------|----------------------------------------|--|--|--|

| SR1 | SR0 | FROM FULL<br>VOLUME TO MUTE | FROM FULL<br>VOLUME TO<br>VMN = 1 (ms) |  |  |  |

| 0   | 0   | 63µs                        | 0.1                                    |  |  |  |

| 0   | 1   | 125ms                       | 200                                    |  |  |  |

| 1   | 0   | 63ms                        | 100                                    |  |  |  |

| 1   | 1   | 42ms                        | 67                                     |  |  |  |

Set MUTE = 1 in the volume register (register 0x2, bit B7) to mute the headphone amplifiers. The mute function is independent of the volume control. The programmed volume settings are not reset when mute is enabled. With the zero-crossing detection and volume slew enabled, the Mute command mutes the output after the first zero crossing or after a 200ms timeout (SR = 01).

#### Mono Mode

Set MONO = 1 in the general-purpose register (register 0x3, bit B2) to enable mono mode. In mono mode, HPR is disabled, the left and right audio channels are summed and output on HPL. The 6dB attenuation ensures that the summed signal amplitude does not overdrive headphone amplifiers. SMONO in the status B register (register 0x1, bit B4) sets to 1 when the MAX9850 is in mono mode.

#### **Configuring the Headphone and Line Outputs** Set HPEN and LNOEN in the enable register (register 0x5, bits B3 and B2) equal to 1 to enable the headphone outputs (HPR and HPL). Set HPEN or LNOEN = 0 to disable the headphone outputs.

The headphone amplifier inputs are driven from the outputs of the line amplifier. Disabling the line out by setting LNOEN = 0 in the enable register (register 0x5, bit B2), deprives the headphone amplifiers of an input signal and disables the headphone outputs (HPR and HPL).

The internal charge pump must be enabled to operate the headphone and line outputs. Enable the charge pump by programming CPEN(1:0) = 11 in the enable register (register 0x5, bits B5 and B4). See the *Charge Pump* section for more details.

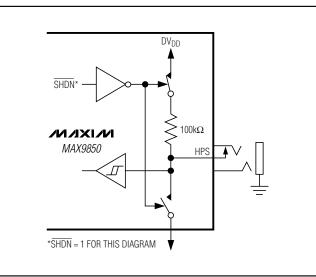

#### **Headphone Sense Input (HPS)**

The headphone sense input (HPS) monitors the headphone jack, and automatically disables the headphone amplifiers based upon the voltage applied at HPS. For automatic headphone detection, connect HPS to the

Figure 2. Headphone Sense (HPS) Input

control pin of a 3-wire headphone jack as shown in Figure 2. With no headphone present, the output impedance of the headphone amplifier pulls HPS to less than 0.3 x DV<sub>DD</sub>. When a headphone is inserted into the jack, the control pin is disconnected from the tip contact and HPS is pulled to DV<sub>DD</sub> through the internal 100k $\Omega$  pullup. No external resistor is required. Leave HPS floating if automatic headphone sensing is not used. HPS must be high and HPEN (register 0x5, bit B3) must be set to 1 for the headphone amplifiers (HPR and HPL) to output an audio signal.

The MAX9850 includes an HPS debounce circuit that ignores short duration changes on HPS. The debounce circuit ensures that a headphone is properly connected before powering up and enabling the headphone amplifiers. Program DBDEL(1:0) in the general-purpose register (register 0x3, bits B4 and B3) to set the HPS debounce delay time. The delay time is based on a division of the charge-pump frequency, fcp. See the *Charge Pump* section for details on programming the charge-pump frequency. Table 2 lists the available delay times of the debounce circuit.

There is no delay on removal of a headphone when using automatic headphone sense. The headphone amplifiers are immediately placed into shutdown when HPS goes high.

SHPS in the status A register (register 0x0, bit B4) reports the status of HPS. SHPS = 0 when HPS is low and SHPS = 1 when HPS is high.

| DBDEL(0) | DBDEL(0) | DEBOUNCE<br>TIME<br>(ms)              | DEBOUNCE TIME<br>BASED ON<br>f <sub>CP</sub> = 667kHz (ms) |

|----------|----------|---------------------------------------|------------------------------------------------------------|

| 0        | 0        | 0                                     | 0 (Disabled)                                               |

| 0        | 1        | 2 <sup>17</sup> x 1 / f <sub>CP</sub> | Approx 200                                                 |

| 1        | 0        | 2 <sup>18</sup> x 1 / f <sub>CP</sub> | Approx 400                                                 |

| 1        | 1        | 2 <sup>19</sup> x 1 / f <sub>CP</sub> | Approx 800                                                 |

#### **Table 2. HPS Debounce Times**

#### **GPIO**

Configure GPIO as an input or an output with the GPD bit in the general-purpose register (register 0x3, bit B5). GPD = 1 configures GPIO as an open-drain output while GPD = 0 makes GPIO an input. Connect an external pullup resistor from GPIO to  $DV_{DD}$  when GPIO is configured as an output.

GPIO as an output allows the MAX9850 to drive an LED or other state indicator. It also can be used to provide an interrupt signal to alert a  $\mu$ C when an event has occurred. Potential events include changes in internal PLL lock state, connecting headphones to HPS, headphone outputs reaching the minimum volume, or an overcurrent on the headphone outputs. Any of these events can be programmed to pulse GPIO's output state when GPIO is configured as an open-drain output.

Using GPIO as an input allows the MAX9850 to receive a signal from a  $\mu$ C's digital I/O or other device. The status of GPIO is read through SGPIO in the status A register (register 0x0, bit B6).

#### GPIO as an Output

Set GPD = 1 (register 0x3, bit B5) to configure GPIO as an output. Program the output operating mode of GPIO with GM(1:0) in the general-purpose register (register 0x3, bits B7 and B6). GPIO can be programmed to output logic-high, a logic-low, or it can be programmed to output an interrupt signal by changing state when the ALERT bit in the status A register (register 0x0, bit B7) sets. Table 3 lists GPIO's modes of operation.

# Table 3. GPIO Output Operating Modes (GPD = 1)

| GM(1) | GM(0) | MODE DESCRIPTION                                     |  |  |  |

|-------|-------|------------------------------------------------------|--|--|--|

| 0     | 0     | GPIO = 0                                             |  |  |  |

| 0     | 1     | GPIO = High impedance                                |  |  |  |

| 1     | 0     | GPIO = 0, ALERT output pulse enabled                 |  |  |  |

| 1     | 1     | GPIO = High impedance, ALERT output pulse<br>enabled |  |  |  |

#### Table 4. Interrupt Enable Register (0x4) Events

| EVENT                                                                                                                                                   | BIT NUMBER IN REGISTER 0x4 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| LCK (register 0x0, bit B5) sets when the internal PLL acquires or loses frequency lock                                                                  | В5                         |

| SHPS (register 0x0, bit B4) sets after the headphone is inserted and the debounce time has elapsed when the headphone amplifier is powered up and ready | B4                         |

| VMN (register 0x0, bit B3) sets when the headphone amplifier minimum volume is reached                                                                  | В3                         |

| IOHL or IOHR (register 0x0, bits B1 or B0) sets after an overcurrent at either HPL or HPR                                                               | BO                         |

The interrupt enable register programs the MAX9850 to set ALERT = 1 when an event occurs. GPIO pulses when ALERT sets if GM(1:0) is programmed with 10 or 11. Table 4 contains a list of events that can set ALERT and their corresponding bit positions in the interrupt enable register. Enable the interrupt for each event by setting its bit to 1.

GPIO as an Input

The state of the GPIO input is read through SGPIO in the status A register (register 0x0, bit B6). Set ISGPIO = 1 to allow ALERT to set when SGPIO changes state.

#### **Internal Timing**

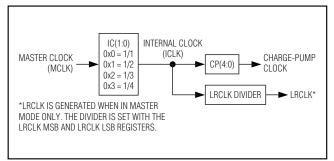

The internal clock (ICLK) and sample rate clock (LRCLK in master mode) are derived from MCLK. The MAX9850's flexible operating modes allow any desired LRCLK sample rate to operate over a wide range of MCLK input frequencies.

Figure 3 shows a flowchart detailing how the internal clocks are derived from MCLK. The MAX9850 generates ICLK by dividing the MCLK frequency. Higher ICLK frequencies allow for greater DAC oversampling and SNR performance. Dynamic range of 90dB (typ) is possible when f<sub>ICLK</sub> is greater than or equal to 12MHz. Lower ICLK frequencies may require slightly less supply current but sacrifice dynamic range. See the SNR vs. MCLK Frequency graph in the *Typical Operating Characteristics*.

ICLK is a frequency-scaled version of MCLK that is used by the MAX9850 to clock the internal DAC circuitry and generate LRCLK and BCLK when in master mode. The charge-pump clock is derived from ICLK when the internal charge-pump oscillator is not used.

Connect an available system clock to MCLK, see the *DAC Operating Modes* section. MCLK can be supplied from any synchronous or available asynchronous system clock whose frequency falls within the 8.448MHz to 13MHz, or 16.896MHz to 40MHz range. Any MCLK within these ranges allow the MAX9850 to operate at any sample rate between 8kHz to 48kHz in either a master or slave mode of operation. Other MCLK frequencies can still be used, but will limit the sample rate ranges that the MAX9850 operates with as illustrated in Table 5.

Higher ICLK frequencies provide higher SNR. Always use the highest acceptable ICLK. Sample rates other than those listed in Table 5 can be used. The MAX9850 defaults to IC(1:0) = 0x0 at power-up.

#### **DAC Operating Modes**

Four DAC operating modes: master integer, slave integer, master noninteger, and slave noninteger allow flexibility for operating with various applications and virtually any available MCLK frequency within the system. The operating modes are set with MAS in the digital audio register (register 0xA, bit B7) and INT in the LRCLK MSB register (register 0x8, bit B7). Table 6 shows the four modes of operation and the equations needed to program the MAX9850 to use the DAC modes.

The master and slave integer modes are the modes in which DACs commonly operate. In these modes, LRCLK is ICLK divided by an integer value. A typical application would set MCLK equal to 256 x LRCLK. The MAX9850 requires that ICLK be an integer multiple of 16 x LRCLK where the integer multiple is at least 10 when in master or slave integer modes. Integer mode always provides the maximum full-scale signal level performance compared to other modes of operation. Choose integer mode over any other mode of operation when possible.

The master noninteger mode allows for a condition where LRCLK and ICLK may not be related by an integer value. In these modes, the MAX9850 can operate from any available MCLK in the system.

Figure 3. Internally Generated Clock Signals Derived from MCLK

MNXI/M

#### Table 5. Acceptable MCLK Frequency Ranges

|                | MINIMUM ICLK<br>(MHz)                       |                                                   | MAXIMUM ICLK<br>(MHz) | ACC                         | CEPTABLE MC<br>(M             | LK FREQUENC<br>Hz)            | IES*                          |

|----------------|---------------------------------------------|---------------------------------------------------|-----------------------|-----------------------------|-------------------------------|-------------------------------|-------------------------------|

| LRCLK<br>(kHz) | INTEGER MODE<br>(160 x f <sub>LRCLK</sub> ) | NONINTEGER<br>MODE<br>(176 x f <sub>LRCLK</sub> ) | ANY MODE              | IC(1:0) = 0x0<br>SF = 1     | IC(1:0) = 0x1<br>SF = 2       | IC(1:0) = 0x2<br>SF = 3       | IC(1:0) = 0x3<br>SF = 4       |

| 8              | 1.280                                       | 1.4080                                            | 13.0                  | 1.280 and<br>1.4080 to 13.0 | 2.560 and<br>2.8160 to 26.0   | 3.840 and<br>4.2240 to 39.0   | 5.120 and<br>5.6320 to 40.0   |

| 11.025         | 1.764                                       | 1.9404                                            | 13.0                  | 1.764 and<br>1.9404 to 13.0 | 3.528 and<br>3.8808 to 26.0   | 5.292 and<br>5.8212 to 39.0   | 7.056 and<br>7.7616 to 40.0   |

| 12             | 1.920                                       | 2.1120                                            | 13.0                  | 1.920 and<br>2.1120 to 13.0 | 3.840 and<br>4.2240 to 26.0   | 5.760 and<br>6.3360 to 39.0   | 7.680 and<br>8.4480 to 40.0   |

| 16             | 2.560                                       | 2.8160                                            | 13.0                  | 2.560 and<br>2.8160 to 13.0 | 5.120 and<br>5.6320 to 26.0   | 7.680 and<br>8.4480 to 39.0   | 10.240 and<br>11.2640 to 40.0 |

| 22.05          | 3.528                                       | 3.8808                                            | 13.0                  | 3.528 and<br>3.8808 to 13.0 | 7.056 and<br>7.7616 to 26.0   | 10.584 and<br>11.6424 to 39.0 | 14.112 and 15.5232 to 40.0    |

| 24             | 3.840                                       | 4.2240                                            | 13.0                  | 3.840 and<br>4.2240 to 13.0 | 7.680 and<br>8.4480 to 26.0   | 11.520 and 12.6720 to 39.0    | 15.360 and<br>16.8960 to 40.0 |

| 32             | 5.120                                       | 5.6320                                            | 13.0                  | 5.120 and<br>5.6320 to 13.0 | 10.240 and<br>11.2640 to 26.0 | 15.360 and<br>16.8960 to 39.0 | 20.480 and 22.5280 to 40.0    |

| 44.1           | 7.056                                       | 7.7616                                            | 13.0                  | 7.056 and<br>7.7616 to 13.0 | 14.112 and<br>15.5232 to 26.0 | 21.168 and<br>23.2848 to 39.0 | 28.224 and 31.0464 to 40.0    |

| 48             | 7.680                                       | 8.4480                                            | 13.0                  | 7.680 and<br>8.4480 to 13.0 | 15.360 and<br>16.8960 to 26.0 | 23.040 and<br>25.3440 to 39.0 | 30.720 and 33.7920 to 40.0    |

\*The first frequency listed is the minimum MCLK frequency required to operate in integer mode. The range of frequencies indicates the MCLK frequencies the MAX9850 needs to operate in any mode.

#### **Table 6. DAC Operating Modes**

|                                                                                                    |                                                       | SLAVE MODE<br>(MAS = 0)                                          | MASTER MODE<br>(MAS = 1)                                                      |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------|

| MODE                                                                                               |                                                       | LRCLK and BCLK signals supplied from external source             | LRCLK and BCLK signals supplied<br>by MAX9850                                 |

|                                                                                                    |                                                       | Asynchronous                                                     | Asynchronous                                                                  |

| NONINTEGER<br>MODE (INT = 0)                                                                       | LRCLK may be any frequency within an acceptable range | $N_{MSB,LSB} = 0$                                                | $N_{\text{MSB,LSB}} = \frac{2^{22} \times f_{\text{LRCLK}}}{f_{\text{ICLK}}}$ |

| INTEGER MODE<br>(INT = 1) ICLK and LRCLK must be<br>synchronous and exact integer<br>ratio related |                                                       | Synch<br>N <sub>LSB</sub> = $\frac{f_{ICLK}}{16 \times f_{LRC}}$ | ronous<br>, N <sub>MSB</sub> = 0<br>cLK                                       |

M/IXI/M

Slave modes of operation allow the MAX9850 to operate in any audio system where the LRCLK and BCLK must be supplied from an external source. When operating in slave mode, the MCLK supplied to the MAX9850 may be either synchronous or asynchronous with LRCLK. Use the slave integer mode if ICLK is synchronous and has an integer multiple of 16 x LRCLK. Integer mode ensures that the highest levels of full-scale-input signal performance can be achieved. Slave noninteger mode offers the highest degree of clock flexibility. ICLK does not need to be synchronous or an integer multiple of LRCLK when operating in slave noninteger mode.

Master modes of operation allow the MAX9850 to generate and supply an LRCLK and BCLK to other elements in the system. Use master integer mode if the provided ICLK is an integer multiple of 16 x LRCLK. Integer mode ensures that the highest levels of full-scale input signal performance can be achieved. Master noninteger mode allows the MAX9850 to supply virtually any frequency LRCLK with an accuracy better than  $\pm 0.5\%$ .

The slave noninteger mode provides maximum flexibility for ICLK and LRCLK frequencies. The ICLK and LRCLK can be asynchronous and noninteger related. Connect any available system clock that is listed on Table 5 in the *Internal Timing* section. In slave noninteger mode, the acceptable MCLK frequency range is the same as master mode.

#### Master Integer Mode (MAS = 1, IM = 1)

The MAX9850 generates the LRCLK and BCLK in master mode. LRCLK is an integer factor of ICLK by the following equation:

$$f_{LRCLK} = \frac{f_{ICLK}}{16 \times N_{LSB}}$$

where:

$f_{ICLK}$  = ICLK frequency.  $f_{ICLK}$  must be at least 160 x  $f_{LRCLK}$  for proper DAC operation.

$N_{LSB}$  = decimal value of the data contained in LSB(7:0) (register 0x9, bits B7–B0).

$f_{LRCLK} = LRCLK$  frequency.

For example:

$f_{\rm ICLK}$  = 12.228MHz and  $N_{\rm LSB}$  = 16 (0x10),  $f_{\rm LRCLK}$  = 48kHz.

Solve the above equation for NLSB. Use master integer mode if NLSB is an integer. Use master noninteger mode if NLSB is not an integer.

#### Slave Integer Mode (MAS = 0, IM = 1)

The MAX9850 accepts LRCLK and BCLK from an external digital audio source when in slave integer mode. LRCLK must be an **exact** integer multiple of ICLK to ensure proper operation. Program LSB(7:0) (register 0x9, bits B7–B0) with the LRCLK division ratio. Use the following equation to find the value that needs to be programmed to LSB(7:0):

$$N_{LSB} = \frac{f_{ICLK}}{16 \times f_{LRCLK}}$$

where:

$f_{ICLK}$  = ICLK frequency.  $f_{ICLK}$  must be 160 x  $f_{LRCLK}$  for proper DAC operation.

$f_{LRCLK}$  = supplied LRCLK frequency.

$N_{LSB}$  = decimal value of the data contained in LSB(7:0) (register 0x9, bits B7–B0).

For example:

$f_{ICLK}$  = 11.2896MHz and  $f_{LRCLK}$  = 44.1kHz,  $N_{LSB}$  = 16 (0x10).

Solve the above equation for  $N_{LSB}$ . Use slave integer mode if  $N_{LSB}$  is an integer. Use slave noninteger mode if  $N_{LSB}$  is not an integer.

#### Slave Noninteger (MAS = 0, IM = 0)

In slave noninteger mode, the MAX9850 accepts an external LRCLK and converts the digital audio signal using any asynchronous ICLK within the acceptable operating range. The MAX9850 uses internal clock recovery circuitry to generate all required internal clocks. This allows the MAX9850 to operate in systems that do not have dedicated clock sources or crystal oscillators. Virtually any existing system clock will work. fICLK must be at least 176 x fLRCLK for proper operation.

#### Master Noninteger Mode (MAS = 1, IM = 0)